因为专业

所以领先

根据最新行业资料,AI算力领域主要采用以下几种先进封装工艺方式,每种技术都有其独特优势和应用场景:

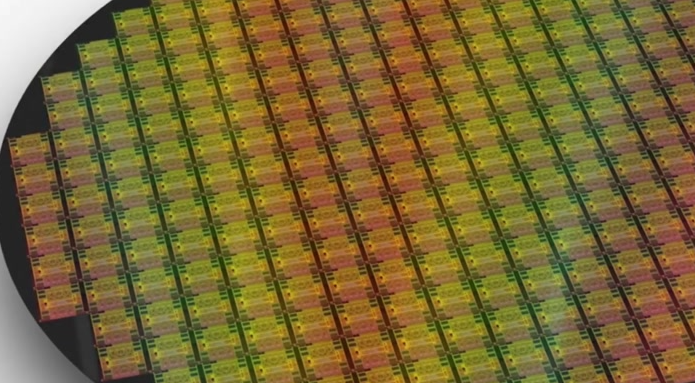

AI算力需求的爆炸式增长,已不再能仅依靠缩小晶体管尺寸来满足。先进封装技术通过将多个芯片(如处理器、内存、加速器)高密度、高性能地集成在一起,已成为提升算力的核心路径。目前主要的先进封装工艺方案,可以按照其技术原理和行业生态来划分:

工作原理:2.5D封装在芯片与基板之间加入硅中介层进行打孔和布线,通过硅通孔(TSV)连接上下表面金属;3D封装则将多个芯片垂直堆叠,通过TSV实现芯片间电气连接。

主要技术:

CoWoS(台积电):将芯片堆叠于硅中介层上再封装于基板,是目前AI芯片最主流的封装方式,全球绝大部分AI芯片厂商采用此技术,目前产能全线满载

SoIC(台积电):3D硅堆叠技术,属于台积电3DFabric平台的前端技术

I-Cube(三星):三星的2.5D封装技术

EMIB(英特尔):嵌入式多芯片互连桥,通过基板内的微型硅桥连接芯片,具有成本效益高、良率提升、生产效率高、尺寸优化等优势

Foveros(英特尔):支持2.5D与3D堆叠,采用TSV与硅中介层,特别适用于客户端与边缘应用场景

优势:提高芯片集成度和性能,缩短互连距离,降低延迟和功耗,突破"内存墙"制约

应用场景:GPU、CPU超算、HBM存储芯片等高性能计算领域

工作原理:将单一复杂芯片拆分为多个小型、独立且可复用的芯粒单元,通过先进封装技术实现不同工艺、材料和功能芯片的灵活组合。

优势:

小芯粒提升晶圆良率,降低生产风险

多芯片分布式架构满足高效能计算和扩展需求

异构芯片的灵活集成提升设计灵活性,有效控制成本

克服单片SoC在光罩尺寸、成本与良率方面的瓶颈

应用场景:AI加速器、高性能计算芯片、异构集成系统

工作原理:通过重构芯片的封装结构,将芯片的I/O引脚重新布局在封装基板的边缘,形成扇出型结构,实现更小的封装尺寸和更高的I/O密度。

主要技术:

Fan-out:晶圆扇出技术

XDFOI™:长电科技自主研发的多维扇出集成技术,已实现4nm Chiplet量产

优势:提高封装可靠性,实现更薄的封装和更多的I/O,使AI芯片能够与其他组件更紧密地集成

应用场景:无线芯片、基带芯片、移动设备、5G与消费电子

工作原理:结合铜-铜和氧化物-氧化物键合,在芯片之间创建高度可靠、低功耗的连接。2021年展示的技术已将间距缩小至3微米。

优势:实现紧密的芯片集成,提高速度并降低功耗,减少占用空间并提高数据传输速率

应用场景:内存和逻辑组件的3D堆叠,需要高速数据移动的AI任务

工作原理:在芯片还在晶圆上的时候就对芯片进行封装,保护层黏接在晶圆的顶部或底部,然后连接电路,再将晶圆切成单个芯片。

类型:

扇入型:RDL走线向内布线,面积受限,约200个I/O和0.6mm将达到上限

扇出型:通过扩展封装的可用面积,RDL走线可以向内和向外布线,实现更薄的封装和更多的I/O

应用场景:移动设备、物联网设备等对尺寸要求严格的场景

工作原理:将多种功能芯片集成为一颗芯片,压缩模块体积、缩短电气连接距离。

优势:通过改变模组及缩小尺寸,为终端产品提供更大的电池空间,集成更多功能;通过异质整合减少组装厂工序,降低产业链复杂度

应用场景:可穿戴设备、XR设备、消费电子等对微型化要求高的领域

工作原理:将芯片功能区朝下以倒扣的方式背对着基板,通过焊料凸点(Bump)与基板进行互联。基础的倒装芯片采用回流焊作为键合方案,此外还有热压焊、超声焊和胶粘连接等方案。

历史:起源于20世纪60年代,由IBM率先研发,是发展时间最长的先进封装技术

应用场景:作为基础互连技术,广泛应用于各种先进封装中

工作原理:使用玻璃材料替代传统有机基板,提供更高的互连密度和平面度。

优势:超低平面度、更好的热稳定性和机械稳定性,能够大幅提高基板上的互连密度

发展现状:英特尔计划在2030年前实现玻璃基板的量产;日本企业Rapidus于2025年SEMICON Japan展会上首次展示采用600 x 600毫米玻璃基板的面板级封装原型,计划2028年前完成技术优化并投入大规模生产

工作原理:将光学器件与电子芯片共同封装,实现光电一体化

优势:在传输损耗、抗干扰能力、带宽容量和能效比方面展现出显著优势

应用场景:高速数据传输、AI数据中心互联

AI算力清洗- 锡膏助焊剂清洗剂介绍:

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用 水基清洗剂产品。

致力于为SMT电子表面贴装清洗、功率电子器件清洗及先进封装清洗提供高品质、高技术、高价值的产品和服务。 (13691709838)Unibright 是一家集研发、生产、销售为一体的国家高新技术、专精特新企业,具有二十多年的水基清洗工艺解决方案服务经验,掌握电子制程环保水基清洗核心技术。水基技术产品覆盖从半导体芯片封测到 PCBA 组件终端的清洗应用。是IPC-CH-65B CN《清洗指导》标准的单位。 全系列产品均为自主研发,具有深厚的技术开发能力,拥有五十多项知识产权、专利,是国内为数不多拥有完整的电子制程清洗产品链的公司。 致力成为芯片、电子精密清洗剂的领先者。以国内自有品牌,以完善的服务体系,高效的经营管理机制、雄厚的技术研发实力和产品价格优势,为国内企业、机构提供更好的技术服务和更优质的产品。 的定位不仅是精湛技术产品的提供商,另外更具价值的是能为客户提供可行的材料、工艺、设备综合解决方案,为客户解决各类高端精密电子、芯片封装制程清洗中的难题,理顺工艺,提高良率,成为客户可靠的帮手。

凭借精湛的产品技术水平受邀成为国际电子工业连接协会技术组主席单位,编写全球首部中文版《清洗指导》IPC标准(标准编号:IPC-CH-65B CN)(“Guidelines for Cleaning of Printed Boards and Assemblies”),IPC标准是全球电子行业优先选用标准,是集成电路材料产业技术创新联盟会员成员。

主营产品包括:集成电路与先进封装清洗材料、电子焊接助焊剂、电子环保清洗设备、电子辅料等。

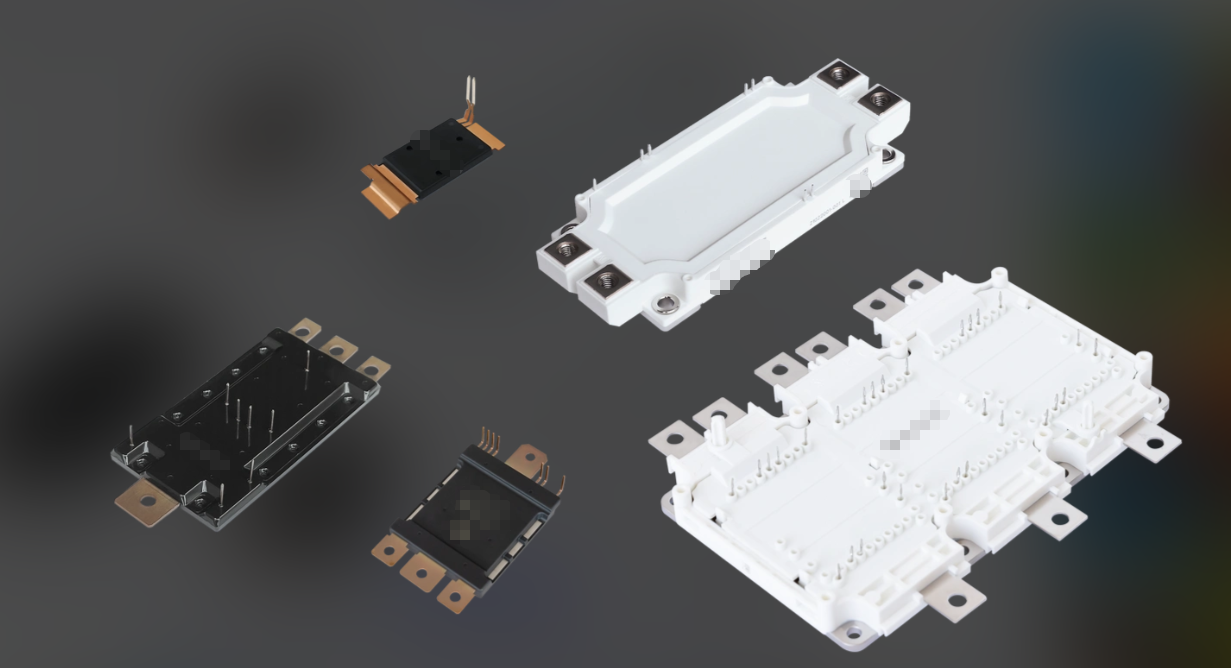

半导体技术应用节点:FlipChip ;2D/2.5D/3D堆叠集成;COB绑定前清洗;晶圆级封装;高密度SIP焊后清洗;功率电子清洗。

![[x]](http://www.cotonix.com/template/default/picture/closeimgfz1.svg)