因为专业

所以领先

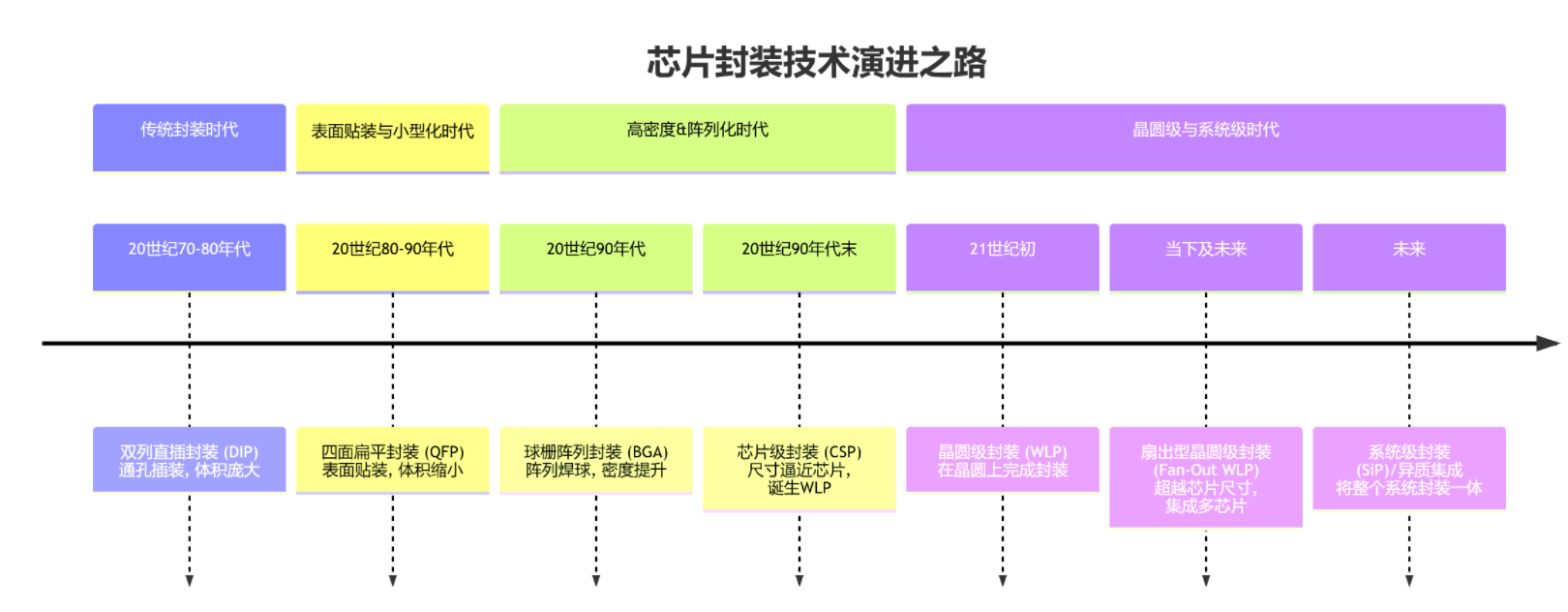

关于芯片制造中封装技术从传统封装到晶圆级封装(WLP)发展晋级阶段的详细阐述。

封装技术的发展史,本质上是一部追求 “更小、更薄、更轻、更快、更省、更可靠” 的历史。它从保护芯片、连接内外世界的简单角色,演进成为提升整个系统性能的关键赋能技术。

整个发展路程可以清晰地分为四个主要阶段,其核心演进方向如下图所示:

时间: 20世纪70-80年代

代表技术: 双列直插封装 (DIP - Dual In-line Package)

特点:

工艺: 封装厂将测试好的晶圆进行“划片”(Dicing),分割成单个芯片(Die)。然后将芯片粘结在引线框架(Lead Frame)上,利用细金属线(金线)进行“键合”(Wire Bonding)连接芯片焊盘和引线框架的引脚,最后用塑料或陶瓷材料封装成型。

安装方式: 通孔插装(Through-hole technology),将封装好的芯片引脚插入印刷电路板(PCB)的通孔中再进行焊接。

局限性:

体积庞大:封装尺寸远大于芯片本身,严重浪费空间。

效率低下:引脚数(Pin Count)受限,难以满足复杂芯片的需求。

电性能差:引线较长,产生较大的寄生电感和电阻,影响信号传输速度和完整性,不适合高频应用。

时间: 20世纪80-90年代

代表技术: 小外形封装 (SOP)、四面扁平封装 (QFP - Quad Flat Package)

特点:

工艺: 仍然主要采用“引线框架 + 键合线”的结构,但引脚从两侧发展到四侧,引脚间距(Pitch)更小。

安装方式: 表面贴装(Surface-mount technology,SMT),引脚直接焊接在PCB表面,无需打孔。

晋级:

体积缩小:封装体积和厚度相比DIP显著减小。

密度提升:引脚数量增加,适应了更复杂芯片(如MCU、早期CPU)的需求。

局限性:

键合线瓶颈:当引脚数进一步增加时,引脚间距已接近工艺极限,易导致焊接短路。

电热性能:键合线的寄生效应仍然是高频性能的瓶颈,散热能力有限。

时间: 20世纪90年代

代表技术:

特点: 定义是封装面积不超过芯片面积的1.2倍。CSP是一种概念,而非单一技术,它可以通过多种方式实现(如引线框架型、柔性基板型等)。

晋级: 实现了封装尺寸的极致小型化,是迈向晶圆级封装(WLP) 的关键过渡。

特点: 将封装引脚从封装体四周改为以阵列形式排布在封装底部的焊球。这些焊球既是电气连接点,也是机械连接点。

晋级:

局限性: 封装尺寸仍然大于芯片本身。

密度飞跃:极大地增加了I/O数量,解决了多引脚芯片的封装难题。

电性能提升:焊点路径短,减少了引线电感和电容,改善了高频性能。

散热更好:芯片背面往往可接触散热器,热管理能力增强。

球栅阵列封装 (BGA - Ball Grid Array)

芯片级封装 (CSP - Chip Scale Package)

时间: 20世纪90年代末至今

核心革命:晶圆级封装 (WLP - Wafer-Level Package)

理念颠覆: 将封装工艺从“单个芯片”层面提前到“整个晶圆”层面完成。在划片之前,直接在晶圆上对所有芯片同时进行再布线(RDL)、凸点制作(Bumping)等封装步骤。完成后,再进行测试和划片。

代表技术:

特点: 突破了芯片面积的限制。通过将芯片嵌入到环氧树脂模塑料(Molding Compound)中,形成一个“重构晶圆”(Reconstituted Wafer)。然后在芯片本体之外的区域进行再布线,将I/O“扇出”到更大的区域。

晋级:

应用: 苹果/高通/海思等旗舰手机处理器、5G毫米波天线模块、高端AI加速器等。

I/O密度更高:可以容纳比Fan-In WLP多得多的I/O数量。

集成度更高:可以在重构晶圆上集成多个不同工艺、不同功能的芯片(如处理器、内存、射频芯片),实现系统级封装(SiP) 和异质集成。

性能更优:互连路径极短,提供了最优的电性能和热性能。

特点: 所有I/O焊球都分布在芯片内部的区域。是最基本、最经济的WLP形式。

优点: 尺寸最小(等于芯片本身),成本低,电性能极佳。

应用: 广泛用于I/O数量较少的芯片,如电源管理IC、射频芯片、手机中的各种传感器等。

扇入型晶圆级封装 (Fan-In WLP)

扇出型晶圆级封装 (Fan-Out WLP) - 当前主流与高地

未来方向:系统级封装 (SiP) 与异构集成 (Heterogeneous Integration)

封装技术的角色已经从“保护芯片”转变为“集成系统”。未来的发展不再是单一技术的竞争,而是融合了Fan-Out WLP、2.5D/3D IC(硅通孔TSV)、嵌入式基板等多项先进技术的平台化竞争,目标是在一个封装体内集成整个电子系统。

| 特性 | 传统封装 (DIP/QFP) | 先进封装 (BGA/CSP) | 晶圆级封装 (WLP) |

| 工艺顺序 | 先划片,后封装 | 先划片,后封装 | 先封装,后划片 |

| 封装尺寸 | 远大于芯片 | 略大于芯片 (~1.2x) | 等于或稍大于芯片 |

| I/O密度 | 低 | 中 | 极高 |

| 电性能 | 差(寄生效应大) | 较好 | 优异(路径最短) |

| 成本导向 | 封装本身成本 | 封装本身成本 | 整体系统成本/性能比 |

| 核心功能 | 保护、连接 | 保护、连接、提升密度 | 保护、连接、提升系统性能与集成度 |

结论:

从传统封装到晶圆级封装的发展路程,是一次从 “后端制造” 到 “前道延伸” 的思维转变,是封装从“被动适应”到“主动赋能”的角色蜕变。晶圆级封装,特别是扇出型(Fan-Out)技术,已经成为推动摩尔定律继续前行、实现异质集成和系统级创新的最重要引擎之一。

晶圆级封装清洗剂-- 芯片封装前锡膏助焊剂清洗剂介绍:

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用 水基清洗剂产品。

致力于为SMT电子表面贴装清洗、功率电子器件清洗及先进封装清洗提供高品质、高技术、高价值的产品和服务。 (13691709838)Unibright 是一家集研发、生产、销售为一体的国家高新技术、专精特新企业,具有二十多年的水基清洗工艺解决方案服务经验,掌握电子制程环保水基清洗核心技术。水基技术产品覆盖从半导体芯片封测到 PCBA 组件终端的清洗应用。是IPC-CH-65B CN《清洗指导》标准的单位。 全系列产品均为自主研发,具有深厚的技术开发能力,拥有五十多项知识产权、专利,是国内为数不多拥有完整的电子制程清洗产品链的公司。 致力成为芯片、电子精密清洗剂的领先者。以国内自有品牌,以完善的服务体系,高效的经营管理机制、雄厚的技术研发实力和产品价格优势,为国内企业、机构提供更好的技术服务和更优质的产品。 的定位不仅是精湛技术产品的提供商,另外更具价值的是能为客户提供可行的材料、工艺、设备综合解决方案,为客户解决各类高端精密电子、芯片封装制程清洗中的难题,理顺工艺,提高良率,成为客户可靠的帮手。

凭借精湛的产品技术水平受邀成为国际电子工业连接协会技术组主席单位,编写全球首部中文版《清洗指导》IPC标准(标准编号:IPC-CH-65B CN)(“Guidelines for Cleaning of Printed Boards and Assemblies”),IPC标准是全球电子行业优先选用标准,是集成电路材料产业技术创新联盟会员成员。

主营产品包括:集成电路与先进封装清洗材料、电子焊接助焊剂、电子环保清洗设备、电子辅料等。

半导体技术应用节点:FlipChip ;2D/2.5D/3D堆叠集成;COB绑定前清洗;晶圆级封装;高密度SIP焊后清洗;功率电子清洗。

![[x]](/template/default/picture/closeimgfz1.svg)