因为专业

所以领先

我们来对台积电(TSMC)两大核心先进封装技术——CoWoS和InFO进行详细的解析和对比。

这两种技术是台积电从一家纯晶圆制造厂(Foundry)转型为“晶圆制造与封装服务提供商”的关键,开启了“后摩尔定律”时代,通过封装技术来持续提升芯片性能。

传统封装(Package)是将制造好的芯片(Die)放入封装基板,用引线键合(Wire Bonding)的方式连接引脚,主要起保护、连接和散热的作用。

先进封装(Advanced Packaging) 则更侧重于:

提升互联密度:用更短、更密集的互连(如硅通孔TSV、再布线层RDL)替代长引线,显著减少延迟和功耗。

异质集成(Heterogeneous Integration):将不同工艺节点、不同功能、甚至不同材质的芯片(如CPU、GPU、HBM、射频芯片等)集成在一个封装内,实现类似单芯片的性能。

缩小整体尺寸:尤其对于移动设备,在提升性能的同时保持小巧外形。

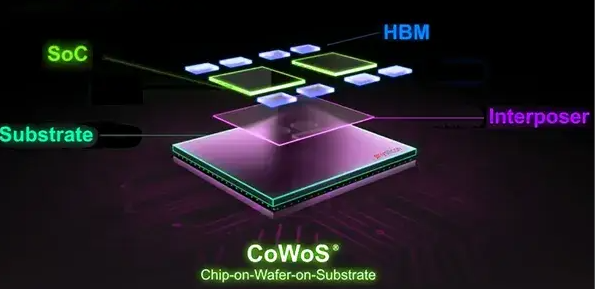

CoWoS是台积电2.5D先进封装技术的旗舰和开创者,最初为NVIDIA的GPU和AMD的处理器与高带宽内存(HBM)集成而开发。

CoWoS的核心是在芯片和封装基板之间插入一个“硅中介层(Silicon Interposer)”。这个中介层是CoWoS技术的精髓。

结构分解:

Chip (Die): 计算芯片,如CPU、GPU、ASIC等。

Wafer (Interposer): 硅中介层。这是一片经过特殊加工的硅片,上面制作有高密度的互连线(Micro Wiring)和硅通孔(TSV - Through-Silicon Via)。

Substrate: 传统的有机封装基板,连接中介层和PCB主板。

关键工艺步骤:

制造硅中介层:在硅晶圆上利用前道半导体工艺(光刻、刻蚀、沉积)制作出极其精细的金属互连层(线宽/线距可达亚微米级别)。

加工TSV:在中介层上刻蚀出通孔并填充导电材料(如铜),这是连接上下层的垂直通道。

Chip on Wafer (CoW):将多个预先制造好的芯片(如GPU Die和HBM Die)通过微凸块(Microbump) 以超高精度倒装焊(Flip-Chip)的方式键合到硅中介层上。这一步是在晶圆(Wafer)级别完成的。

封装与测试:将键合好芯片的整个中介层切割成单个单元,然后通过更大的焊料凸块(C4 Bump) 倒装焊到有机封装基板上。

最终封装:加盖、注塑成型、安装散热器等,完成最终封装。

极高的互联密度和带宽:硅中介层上的线路可以做得像芯片内部一样精细,远超任何有机基板的能力。这使得多个芯片(如逻辑芯片和HBM)之间可以实现数千条超短距离、低功耗的互连,提供极高的带宽(这也是HBM得以实现的基础)。

优异的热性能和信号完整性:硅的热膨胀系数(CTE)与芯片本身非常接近,减少了热应力。硅中介层的屏蔽作用也改善了信号完整性。

强大的异质集成能力:可以集成来自不同晶圆厂、不同工艺节点的芯片。

高性能计算(HPC):NVIDIA的A100、H100系列GPU;AMD的MI系列加速卡;NVIDIA的Blackwell架构B200 GPU。

人工智能(AI)/机器学习(ML)加速器:Google的TPU、Xilinx(AMD)的FPGA等。

高端网络芯片:需要极高吞吐量的交换机和路由器芯片。

CoWoS本身也在迭代:

CoWoS-S:最经典的版本,使用Silicon Interposer(硅中介层)。

CoWoS-R:使用RDL(再布线层)代替硅中介层,成本更低,适用于互联密度要求稍低的场景。

CoWoS-L:Local Silicon Interposer(局部硅中介层)与RDL混合使用,在需要高密度互联的区域(如芯片之间)使用小块硅中介层,其他区域用RDL,平衡了性能和成本。

InFO是台积电的另一项开创性技术,属于扇出型(Fan-Out)封装。它最初是为了满足苹果iPhone处理器对更薄、性能更好、集成度更高的封装需求而开发的。

InFO技术的核心是去掉了中介层和封装基板,直接利用环氧塑封料(EMC) 重构一个“假”的晶圆,并在上面制作高密度的再布线层(RDL - Redistribution Layer) 来连接多个芯片和对外引脚。

结构分解:

芯片(Die):被集成的芯片。

塑封料(EMC):包裹芯片,形成重构晶圆。

再布线层(RDL):在塑封体表面制作的铜金属布线层,将芯片的触点“扇出”到更广的面积上,并实现芯片间的互连。

焊球(Solder Ball):直接连接到RDL上,用于连接PCB主板。

关键工艺步骤:

载板贴装:将芯片(正面朝下)临时粘贴在一个载板(Carrier)上。

模塑(Molding):用环氧塑封料(EMC)灌注并加热固化,将芯片包裹起来,形成一个“重构晶圆(Reconstituted Wafer)”。

移除载板:将重构晶圆从临时载板上取下,露出芯片背面和埋入的芯片正面触点。

制作RDL:在塑封后的晶圆表面进行薄膜沉积、光刻、电镀等工序,制作出多层精细的铜布线(RDL),这些布线将各个芯片的触点连接起来,并引到更大的节距上。

植球:在RDL上制作焊球。

切割:将重构晶圆切割成单个封装体。

更薄、更轻、尺寸更小:由于省去了中介层和封装基板,InFO封装的高度和尺寸显著减小,非常适合移动设备。

性能更优:互连路径更短,减少了电感和电阻,提升了电源完整性和信号性能,降低了功耗。

成本潜力:省去了昂贵的硅中介层和部分基板,在量大时具有成本优势。

设计灵活性高:RDL层可以按需设计,支持不同数量、不同尺寸的芯片集成。

移动应用处理器(AP):苹果的A系列和M系列芯片(如A11到最新的A17 Pro,M1等)是InFO技术的最大用户。

射频芯片、电源管理芯片(PMIC)、网络芯片等。

物联网(IoT)和可穿戴设备:对尺寸和功耗有极致要求的领域。

InFO-PoP:最具代表性的变体。Package on Package。在处理器芯片的InFO封装顶部再堆叠一颗DRAM内存芯片(如LPDDR)。这大大节省了手机主板空间,已成为高端手机的标准方案。

InFO_oS:On Substrate,用于HPC领域,将多个芯片集成在更大的InFO封装中,然后放在基板上,对标CoWoS,但成本更低。

| 特性 | CoWoS (2.5D) | InFO (Fan-Out) |

| 核心结构 | 硅中介层(Silicon Interposer) + TSV | 再布线层(RDL) + 环氧塑封料(EMC) |

| 互联密度 | 极高(中介层线宽/线距<1μm) | 高(RDL线宽/线距~2-10μm),但低于CoWoS |

| 性能 | 极致性能,专为超高带宽(如HBM)设计 | 优秀,互连短,电性能好,但带宽上限不及CoWoS |

| 厚度/尺寸 | 较厚(有中介层和基板) | 极薄(无中介层和基板),尺寸小 |

| 成本 | 非常高(使用了硅晶圆工艺) | 相对较低(省去硅中介层,使用晶圆级封装) |

| 主要应用 | HPC, AI, 高端GPU/CPU (NVIDIA, AMD) | 移动AP, 射频, IoT (Apple, Qualcomm, Mediatek) |

| 典型产品 | NVIDIA H100 GPU, AMD MI300 | Apple A17 Pro, 麒麟9000S |

CoWoS和InFO是台积电针对不同市场赛道打造的两把利剑:

CoWoS 是 “性能王者”,不惜成本追求极致的互联带宽和计算性能,服务于数据中心、AI等高端市场。

InFO 是 “集成与效率大师”,在有限的空间内实现高度集成和优良性能,主打移动消费电子市场,平衡了性能、尺寸和成本。

两者并非替代关系,而是互补共存。它们共同构成了台积电在先进封装领域的强大护城河,使其能够为客户提供从前沿芯片制造到高端封装的“一条龙”服务,这也是台积电维持其技术领导地位的关键战略之一。随着技术的发展,两者也在相互借鉴和融合(如CoWoS-L和InFO_oS),以满足日益复杂的异质集成需求。

![[x]](/template/default/picture/closeimgfz1.svg)